服务热线:0755- 83387360

产品介绍

产品介绍

The 74HC595; 74HCT595 is an 8-bit serial-in/serial or parallel-out shift register with a storage register and 3-state outputs. Both the shift and storage register have separate clocks. The device features a serial input (DS) and a serial output (Q7S) to enable cascading and an asynchronous reset MR input. A LOW on MR will reset the shift register. Data is shifted on the LOW-to-HIGH transitions of the SHCP input. The data in the shift register is transferred to the storage register on a LOW-to-HIGH transition of the STCP input. If both clocks are connected together, the shift register will always be one clock pulse ahead of the storage register. Data in the storage register appears at the output whenever the output enable input (OE) is LOW. A HIGH on OE causes the outputs to assume a high-impedance OFF-state. Operation of the OE input does not affect the state of the registers. Inputs include clamp diodes. This enables the use of current limiting resistors to interface inputs to voltages in excess of VCC.

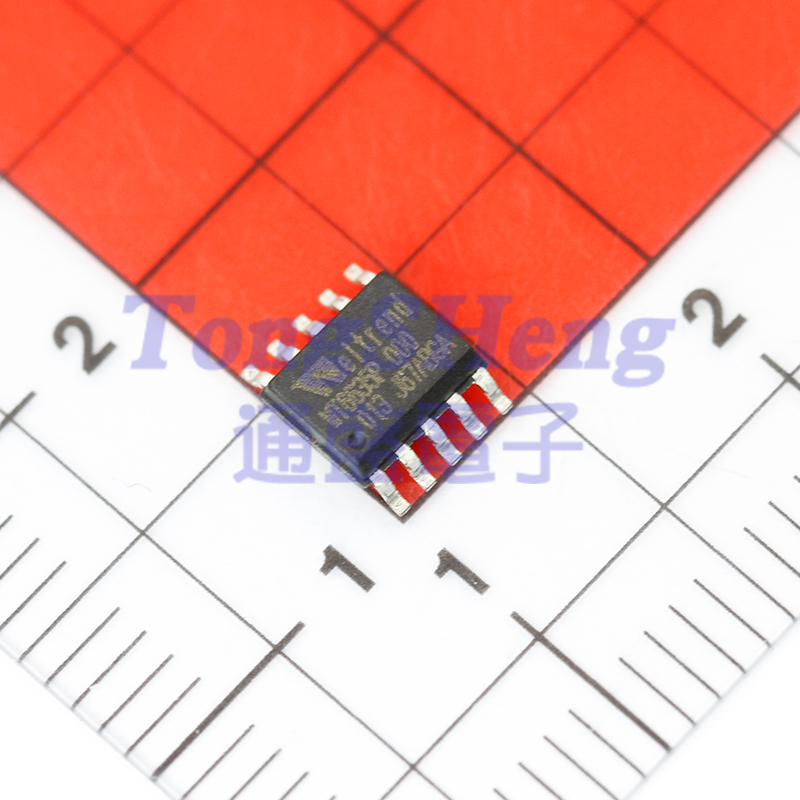

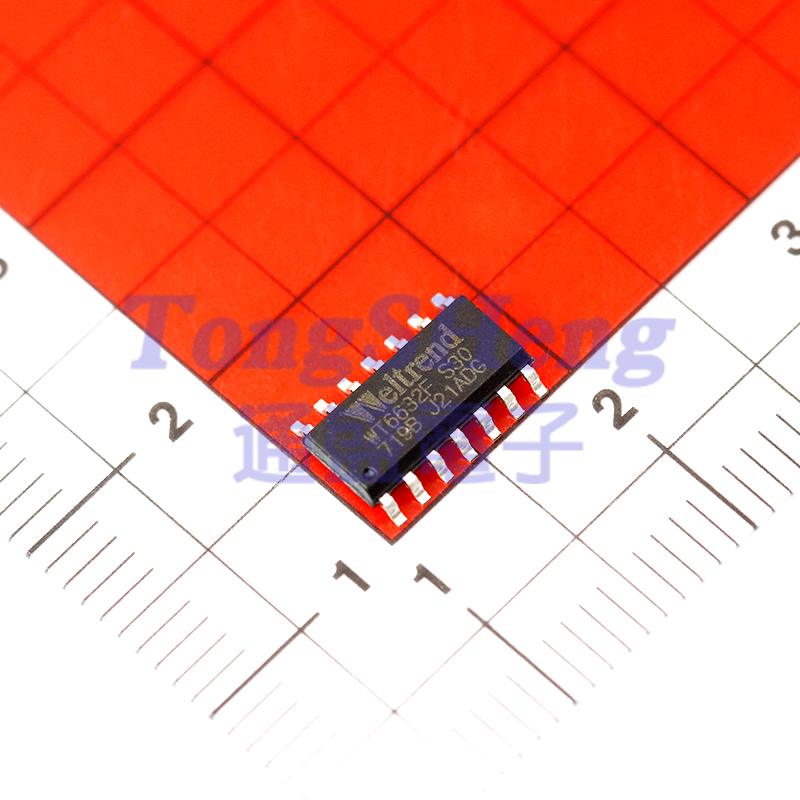

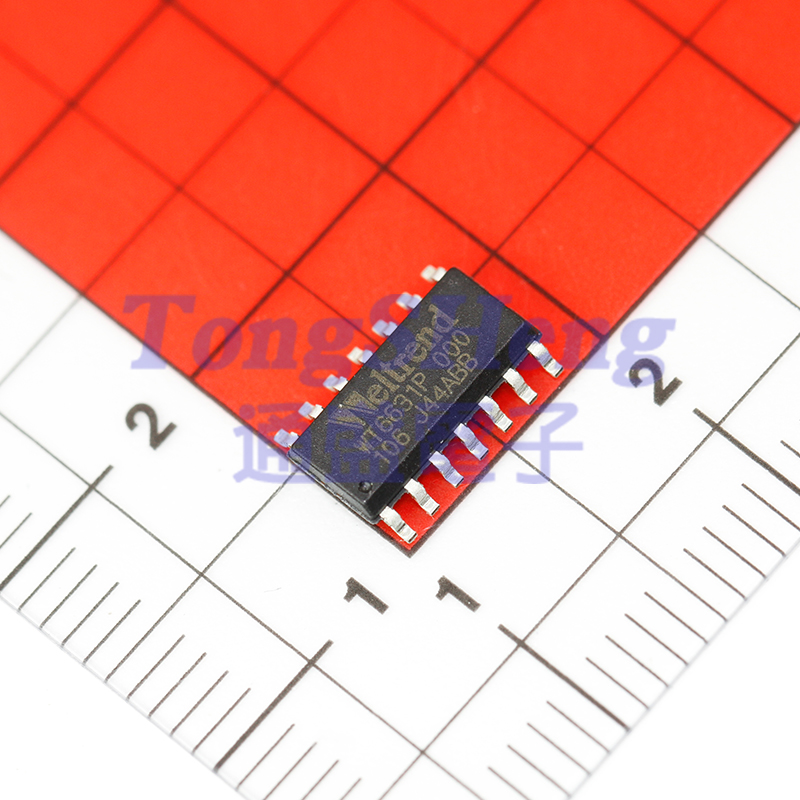

订购信息

订购信息

| 器件类目 |

产品型号 |

封装描述 |

环境温度 |

应 用 | 丝 印 |

| 逻辑IC | 74HC595D |

SO16 |

40~+125℃ |

从串行到并行的数据转换、遥控保持寄存器

|

74HC595D |

波形和厕所电路

波形和厕所电路

产品特性

产品特性

应用范围

应用范围

原装现货,技术选型

云仓现货,快速配送

品类齐全,性能优良

工厂直销,样品申请

荣誉资质

荣誉资质